#### **Not Intended For New Designs**

August 1992

# 11C90/11C91 650 MHz Prescalers

### **General Description**

The 11C90 and 11C91 are high-speed prescalers designed specifically for communication and instrumentation applications. All discussions and examples in this data sheet are applicable to the 11C91 as well as the 11C90.

The 11C90 will divide by 10 or 11 and the 11C91 by 5 or 6, both over a frequency range from DC to typically 650 MHz. The division ratio is controlled by the Mode Control. The divide-by-10 or -11 capability allows the use of pulse swallowing techniques to control high-speed counting modulos by lower-speed circuits. The 11C90 may be used with either ECL or TTL power supplies.

In addition to the ECL outputs Q and  $\overline{Q}$ , the 11C90 contains an ECL-to-TTL converter and a TTL output. The TTL output operates from the same  $V_{CC}$  and  $V_{EE}$  levels as the counter, but a separate pin is used for the TTL circuit  $V_{EE}$ . This minimizes noise coupling when the TTL output switches and

also allows power consumption to be reduced by leaving the separate  $V_{\mbox{\footnotesize{EE}}}$  pin open if the TTL output is not used.

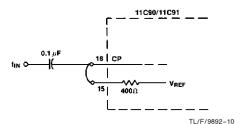

To facilitate capacitive coupling of the clock signal, a  $400\Omega$  resistor (V<sub>REF</sub>) is connected internally to the V<sub>BB</sub> reference. Connecting this resistor to the Clock Pulse input (CP) automatically centers the input about the switching threshold. Maximum frequency operation is achieved with a 50% duty cycle.

Each of the Mode Control inputs is connected to an internal 2  $k\Omega$  resistor with the other end uncommitted (RM $_1$  and RM $_2$ ). An M input can be driven from a TTL circuit operating from the same  $V_{CC}$  by connecting the free end of the associated 2  $k\Omega$  resistor to  $V_{CCA}$ . When an M input is driven from the ECL circuit, the 2  $k\Omega$  resistor can be left open or, if required, can be connected to  $V_{EE}$  to act as a pull-down resistor.

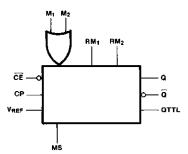

#### **Logic Symbol**

TL/F/9892-2

| Pin Names        | Description                      |

|------------------|----------------------------------|

| CE               | Count Enable Input (Active LOW)  |

| CP               | Clock Pulse Input                |

| M <sub>n</sub>   | Count Modulus Control Input      |

| MS               | Asynchronous Master Set Input    |

| Q, <u>Q</u>      | ECL Outputs                      |

| QTTL             | TTL Output                       |

| RM <sub>n</sub>  | 2 kΩ Resistor to M <sub>n</sub>  |

| V <sub>REF</sub> | 400Ω Resistor to V <sub>BB</sub> |

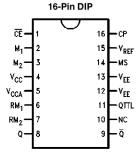

#### **Connection Diagram**

TL/F/9892-1

#### **Absolute Maximum Ratings**

Above which the useful life may be impaired

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Lead Temperature (Soldering, 10 sec.)

Ambient Temperature (T<sub>A</sub>)

Commercial 0°C

Military -55°C

**Recommended Operating**

Min

Supply Voltage (V<sub>EE</sub>) Commercial Military

**Conditions**

-5.7V -5.2V -4.7V -5.7V -5.2V -4.7V

Max

+75°C

+125°C

Тур

## **TTL Input/Output Operation**

#### **DC Electrical Characteristics**

Over Operating Temperature and Voltage Range unless otherwise noted, Pins 12 and 13 = GND

300°C

| Symbol          | Parameter                                                      | Min | Typ<br>(Note 3) | Max  | Units | Conditions                                                                                     |

|-----------------|----------------------------------------------------------------|-----|-----------------|------|-------|------------------------------------------------------------------------------------------------|

| V <sub>IH</sub> | Input HIGH Voltage<br>M <sub>1</sub> and M <sub>2</sub> Inputs |     | 4.1             |      | V     | Guaranteed Input HIGH Threshold<br>Voltage (Note 4), V <sub>CC</sub> = V <sub>CCA</sub> = 5.0V |

| V <sub>IL</sub> | Input LOW Voltage<br>M <sub>1</sub> and M <sub>2</sub> Inputs  |     | 3.3             |      | V     | Guaranteed Input LOW Threshold<br>Voltage (Note 4), V <sub>CC</sub> = V <sub>CCA</sub> = 5.0V  |

| V <sub>OH</sub> | Output HIGH Voltage<br>QTTL Output                             | 2.3 | 3.3             |      | ٧     | $V_{CC} = V_{CCA} = Min,$ $I_{OH} = -640 \mu A$                                                |

| V <sub>OL</sub> | Output LOW Voltage<br>QTTL Output                              |     | 0.2             | 0.5  | ٧     | $V_{CC} = V_{CCA} = Min,$ $I_{OL} = 20.0 \text{ mA}$                                           |

| IIL             | Input LOW Current<br>M <sub>1</sub> and M <sub>2</sub> Inputs  |     | -2.3            | -5.0 | mA    | $V_{CC} = V_{CCA} = Max,$<br>$V_{IN} = 0.4V$ , Pins 6, $7 = V_{CC}$                            |

| Isc             | Output Short Circuit<br>Current                                | -20 | -35             | -80  | mA    | $V_{CC} = V_{CCA} = Max,$<br>$V_{OUT} = 0.0V, Pin 14 = V_{CC}$                                 |

#### **AC Electrical Characteristics**

$V_{CC} = V_{CCA} = 5.0V$  Nominal,  $V_{EE} = GND$ ,  $T_A = +25^{\circ}C$

| Symbol           | Parameter                                     | Min        | Тур        | Max | Units | Conditions                                                                                            |

|------------------|-----------------------------------------------|------------|------------|-----|-------|-------------------------------------------------------------------------------------------------------|

| t <sub>PLH</sub> | Propagation Delay, (50% to 50%)<br>CP to QTTL | 6          | 10         | 14  | ns    | See Figure 1                                                                                          |

| t <sub>PLH</sub> | Propagation Delay, (50% to 50%)<br>MS to QTTL |            | 12         | 17  | ns    |                                                                                                       |

| t <sub>s</sub>   | Mode Control Setup Time                       | 4          | 2          |     | ns    |                                                                                                       |

| t <sub>h</sub>   | Mode Control Hold Time                        | 0          | -2         |     | ns    |                                                                                                       |

| t <sub>TLH</sub> | Output Rise Time<br>(20% to 80%)              |            | 10         |     | ns    |                                                                                                       |

| t <sub>THL</sub> | Output Fall Time<br>(80% to 20%)              |            | 2          |     | ns    |                                                                                                       |

| f <sub>MAX</sub> | Count Frequency                               | 550<br>600 | 650<br>650 |     | MHz   | -55°C to +125°C<br>0°C to +75°C<br>Clock Input AC Coupled<br>350 mV Peak-to-Peak<br>Sinewave (Note 5) |

# **ECL Operation—Commercial Version**

# DC Electrical Characteristics $V_{CC} = V_{CCA} = GND, V_{EE} = -5.2V$

| Symbol           | Parameter                                                                             | Min                     | Тур                  | Max                     | Units | TA                         | Conditions                                        |

|------------------|---------------------------------------------------------------------------------------|-------------------------|----------------------|-------------------------|-------|----------------------------|---------------------------------------------------|

| V <sub>OH</sub>  | Output HIGH Voltage<br>Q and Q                                                        | -1060<br>-1025<br>-980  | -995<br>-960<br>-910 | -905<br>-880<br>-805    | mV    | 0°C<br>+ 25°C<br>+ 75°C    | Load = $50\Omega$ to $-2V$                        |

| V <sub>OL</sub>  | Output LOW Voltage $\overline{Q}$ and $\overline{\overline{Q}}$                       | -1820                   | <b>-1705</b>         | -1620                   | mV    | 0°C to<br>+ 75°C           |                                                   |

| V <sub>IH</sub>  | Input HIGH Voltage                                                                    | -1135<br>-1095<br>-1035 |                      | −840<br>−810<br>−720    | mV    | 0°C<br>+ 25°C<br>+ 75°C    | Guaranteed Input HIGH<br>Signal (Note 6)          |

| V <sub>IL</sub>  | Input LOW Voltage                                                                     | -1870<br>-1850<br>-1830 |                      | -1500<br>-1485<br>-1460 | mV    | 0°C<br>+ 25°C<br>+ 75°C    | Guaranteed Input LOW<br>Signal                    |

| I <sub>IH</sub>  | Input HIGH Current CP Input (Note 1) MS Input M <sub>1</sub> and M <sub>2</sub> Input |                         |                      | 400<br>400<br>250       | μΑ    | + 25°C<br>+ 25°C<br>+ 25°C | $V_{IN} = V_{IHA}$                                |

| I <sub>IL</sub>  | Input LOW Current                                                                     | 0.5                     |                      |                         | μΑ    | + 25°C                     | $V_{IN} = V_{ILB}$                                |

| I <sub>EE</sub>  | Power Supply Current                                                                  | -110<br>-119            | -75                  |                         | mA    | 0°C to<br>+75°C            | Pins 6, 7, 13 not connected                       |

| V <sub>EE</sub>  | Operating Supply<br>Voltage Range                                                     | -5.7                    | -5.2                 | -4.7                    | V     | 0°C to<br>+ 75°C           |                                                   |

| V <sub>REF</sub> | Reference Voltage                                                                     | -1550                   |                      | -1150                   | mV    | + 25°C                     | $V_{RM_1} = V_{RM_2} = -5.2V$ $I_N = -10.0 \mu A$ |

AC Electrical Characteristics  $T_{A}=0^{\circ}C$  to  $+75^{\circ}C,\,V_{CC}=V_{CCA}=GND,\,V_{EE}=-5.2V$

| Symbol                               | Parameter                                  | 0°C  |     | + 25°C |     | + <b>75°C</b> | Units | Conditions                                                                                                       |

|--------------------------------------|--------------------------------------------|------|-----|--------|-----|---------------|-------|------------------------------------------------------------------------------------------------------------------|

| Cymbol                               | rarameter                                  | Тур  | Min | Тур    | Max | Тур           | Omis  | Conditions                                                                                                       |

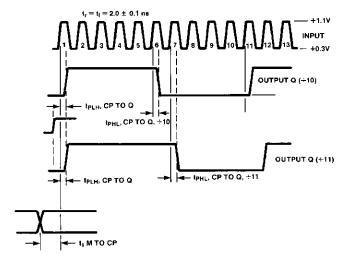

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay,<br>(50% to 50%) CP to Q | 1.8  | 1.3 | 2.0    | 3.0 | 2.5           | ns    | Output: $R_L = 50\Omega$ to $-2.0V$                                                                              |

| t <sub>PLH</sub>                     | Propagation Delay,<br>(50% to 50%) MS to Q | 3.7  |     | 4.0    | 6.0 | 4.5           | ns    | Input: $t_{ri} = t_{fi} = 2.0 \pm 0.1 \text{ ns}$                                                                |

| ts                                   | Setup Time, M to CP                        | 2.0  | 4.0 | 2.0    |     | 2.0           | ns    | (20% to 80%)                                                                                                     |

| t <sub>h</sub>                       | Hold Time, M to CP                         | -2.0 | 0.0 | -2.0   |     | -2.0          | ns    | See Figure 1                                                                                                     |

| t <sub>TLH</sub>                     | Output Rise Time<br>(20% to 80%)           | 1.0  |     | 1.0    | 2.0 | 1.0           | ns    |                                                                                                                  |

| t <sub>THL</sub>                     | Output Fall Time<br>(80% to 20%)           | 1.0  |     | 1.0    | 2.0 | 1.0           | ns    |                                                                                                                  |

| f <sub>MAX</sub>                     | Maximum Clock Frequency                    | 650  | 600 | 650    |     | 625           | MHz   | AC Coupled Input 350 mV<br>Peak-to-Peak. f <sub>MAX</sub> is<br>Guaranteed to be 575 MHz<br>Min at 0°C to +75°C. |

# **ECL Operation—Military Version**

#### **DC Electrical Characteristics**

$V_{CC} = V_{CCA} = GND, V_{EE} = -5.2V$

| Symbol           | Parameter                                                                             | Min                     | Тур                   | Max                  | Units | TA                         | Conditions                                        |

|------------------|---------------------------------------------------------------------------------------|-------------------------|-----------------------|----------------------|-------|----------------------------|---------------------------------------------------|

| V <sub>OH</sub>  | Output HIGH Voltage<br>Q and Q                                                        | -1100<br>-980<br>-910   | -1030<br>-910<br>-820 | -900<br>-820<br>-670 | mV    | −55°C<br>+25°C<br>+125°C   | Load = $100\Omega$ to $-2V$                       |

| V <sub>OL</sub>  | Output LOW Voltage $\overline{\mathbf{Q}}$ and $\overline{\overline{\mathbf{Q}}}$     | -1820                   | <b>-1705</b>          | -1620                | mV    | −55°C to<br>+125°C         |                                                   |

| V <sub>IH</sub>  | Input HIGH Voltage                                                                    | -1190<br>-1095<br>-975  |                       | -905<br>-810<br>-690 | mV    | −55°C<br>+25°C<br>+125°C   | Guaranteed Input HIGH<br>Signal (Note 6)          |

| V <sub>IL</sub>  | Input LOW Voltage                                                                     | -1890<br>-1850<br>-1800 |                       | 1525<br>1485<br>1435 | mV    | −55°C<br>+25°C<br>+125°C   | Guaranteed Input LOW<br>Signal                    |

| I <sub>IH</sub>  | Input HIGH Current CP Input (Note 1) MS Input M <sub>1</sub> and M <sub>2</sub> Input |                         |                       | 400<br>400<br>250    | μΑ    | + 25°C<br>+ 25°C<br>+ 25°C | $V_{IN} = V_{IHA}$                                |

| I <sub>IL</sub>  | Input LOW Current                                                                     | 0.5                     |                       |                      | μΑ    | + 25°C                     | $V_{IN} = V_{ILB}$                                |

| I <sub>EE</sub>  | Power Supply Current                                                                  | -110                    | -75                   |                      | mA    | +25°C                      | Pins 6, 7, 13 not connected                       |

|                  |                                                                                       |                         | -119                  |                      | mA    | −55°C to<br>+125°C         |                                                   |

| V <sub>EE</sub>  | Operating Supply<br>Voltage Range                                                     | -5.7                    | -5.2                  | -4.7                 | V     | −55°C to<br>+125°C         |                                                   |

| V <sub>REF</sub> | Reference Voltage                                                                     | - 1550                  |                       | -1150                | mV    | + 25°C                     | $V_{RM_1} = V_{RM_2} = -5.2V$ $I_N = -10.0 \mu A$ |

#### **AC Electrical Characteristics**

$T_A = -55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ,  $V_{CC} = V_{CCA} = \text{GND}$ ,  $V_{EE} = -5.2\text{V}$

| Symbol                               | Parameter                                  | −55°C |     | + 25°C |     | + 125°C | Units    | Conditions                                                                                                          |

|--------------------------------------|--------------------------------------------|-------|-----|--------|-----|---------|----------|---------------------------------------------------------------------------------------------------------------------|

|                                      | T di dillotoi                              | Тур   | Min | Тур    | Max | Тур     | - Crinto | Conditions                                                                                                          |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay,<br>(50% to 50%) CP to Q | 1.5   | 1.3 | 2.0    | 3.0 | 3.0     | ns       | Output: $R_L = 50\Omega$ to $-2.0V$                                                                                 |

| t <sub>PLH</sub>                     | Propagation Delay,<br>(50% to 50%) MS to Q | 3.5   |     | 4.0    | 6.0 | 5.0     | ns       | Input: $t_{ri} = t_{fi} = 2.0 \pm 0.1 \text{ ns}$                                                                   |

| t <sub>s</sub>                       | Setup Time, M to CP                        | 2.0   | 4.0 | 2.0    |     | 2.0     | ns       | 1 (20% to 80%)                                                                                                      |

| t <sub>h</sub>                       | Hold Time, M to CP                         | -2.0  | 0.0 | -2.0   |     | -2.0    | ns       | See Figure 1                                                                                                        |

| t <sub>TLH</sub>                     | Output Rise Time<br>(20% to 80%)           | 1.0   |     | 1.0    | 2.0 | 1.0     | ns       |                                                                                                                     |

| t <sub>THL</sub>                     | Output Fall Time<br>(80% to 20%)           | 1.0   |     | 1.0    | 2.0 | 1.0     | ns       |                                                                                                                     |

| fMAX                                 | Maximum Clock Frequency                    | 700   | 600 | 650    |     | 600     | MHz      | AC Coupled Input 350 mV<br>Peak-to-Peak. f <sub>MAX</sub> is<br>Guaranteed to be 550 MHz<br>Min at -55°C to +125°C. |

Note 1: Conditions for testing, not shown in the Table, are chosen to guarantee operation under "worst case" conditions.

Note 2: The specified limits represent the "worst case" value for the parameter. Since these "worst case" values normally occur at the temperature and supply voltage extremes, additional noise immunity and guard banding can be achieved by decreasing the allowable system operating ranges.

Note 3: Typical limits are at  $V_{CC} = 5.0 V$  and  $T_A = +25 ^{\circ} C$ .

Note 4: The  $M_1$  and  $M_2$  threshold specifications are normally referenced to the  $V_{CC}$  potential, as shown in the ECL operation tables. Using  $V_{EE}$  (GND) as the reference, as in normal TTL practice, effectively makes the threshold vary directly with  $V_{CC}$ . Threshold is typically 1.3V below  $V_{CC}$  (e.g., +3.7V at  $V_{CC}=+5V$ ). A signal swing about threshold of  $\pm 0.4V$  is adequate, which gives the state  $V_{IH}$  and  $V_{IL}$  values. The internal  $2 \text{ k}\Omega$  resistors are intended to pull TTL outputs up to the required  $V_{IH}$  range, as discussed in the Functional Description and shown in *Figure 5*.

Note 5: TTL Output Signal swing is guaranteed at  $f_{\mbox{\scriptsize MAX}}$  over temperature range.

Note 6:  $M_1$  or  $M_2$  can be tied to  $V_{\mathbb{C}\mathbb{C}}$  for fixed divide-by-ten operation.

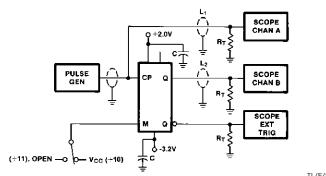

TL/F/9892-3

TL/F/9892-4

#### Conditions:

$\begin{array}{l} V_{CC} = +2.0V \\ V_{EE} = -3.2V \\ R_T = 50\Omega \text{ (scope input impedance)} \\ C_L = \text{Jig and stray capacitance} < 5.0 \text{ pF} \\ I_1 = L_2 = \text{equal } 50\Omega \text{ impedance lines} \\ C = 0.1 \text{ pF} \end{array}$

Note 7: Use high impedance to test QTTL. Connect pin 13 to V<sub>EE</sub>.

Note 8: For High frequency test use AC coupled input as in Figure 3.

Adjust input amplitude to 350 mV peak-to-peak.

FIGURE 1. AC Test Circuit

#### **Functional Description**

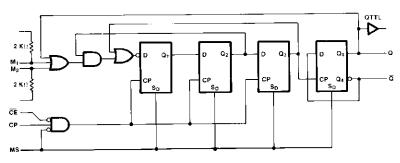

The 11C90 contains four ECL Flip-Flops, an ECL to TTL converter and a Schottky TTL output buffer with an active pull-up. Three of the Flip-Flops operate as a synchronous shift counter driving the fourth Flip-Flop operating as an asynchronous toggle. The internal feedback logic is such that the TTL output and the Q ECL output are HIGH for six clock periods and LOW for five clock periods. The Mode Control (M) inputs can modify the feedback to make the output HIGH for five clock periods and LOW for five clock periods, as indicated in the Count Sequence Table.

The feedback logic is such that the instant the output goes HIGH, the circuit is already committed as to whether the output period will be 10 or 11 clock periods long. This means that subsequent changes in an M input signal, including decoding spikes, will have no effect on the current output period. The only timing restriction for an M input signal is that it be in the desired state at least a setup time before the clock that follows the HHLL state shown in the table. The allowable propagation delay through external logic to an M input is maximized by designing it to use the positive transition of the 11C90 output as its active edge. This gives an allowable delay of ten clock periods, minus the CP to Q delay of the 11C90 and the M to CP setup time. If the external logic uses the negative output transition as its active edge, the allowable delay is reduced to five clock periods minus the previously mentioned delay and setup

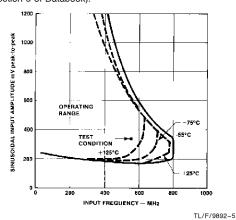

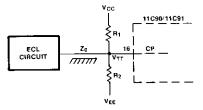

Capacitively coupled triggering is simplified by the  $400\Omega$  resistor which connects pin 15 to the internal V<sub>BB</sub> reference. By connecting this to the CP input, as shown in Figure 3, the clock is automatically centered about the input threshold. A clock duty cycle of 50% provides the fastest operation, since the Flip-Flops are Master-Slave types with offset clock thresholds between master and slave. This feature ensures that the circuit will operate with clock waveforms having very slow rise and fall times, and thus, there is no maximum frequency restriction. Recommended minimum and maximum clock amplitude as a function of a frequency and temperature are shown in the graph labeled Figure 2. When the CP or any other input is driven from another ECL circuit, normal ECL termination methods are recommended. One method is indicated in Figure 4. Other ECL termination methods are discussed in the F100K ECL Design Guide (Section 5 of Databook).

FIGURE 2. AC Coupled Triggering Characteristics

FIGURE 3. Capacitively Coupled Clocking

TL/F/9892-11

| $Z_O\Omega$ | 50   | 75  | 100 |

|-------------|------|-----|-----|

| $R_1\Omega$ | 80.6 | 121 | 162 |

| $R_2\Omega$ | 130  | 196 | 261 |

$V_{EE} = -5.2V$ ,  $V_{CC} = 0V$ ,  $V_{TT} = -2.0V$

#### FIGURE 4. Clocking by ECL Source via Terminated Line

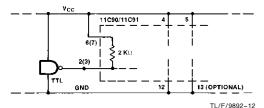

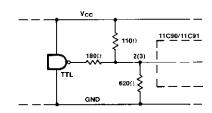

When an M input is to be driven from a TTL output operating from the same  $V_{CC}$  and ground ( $V_{EE}$ ), the internal 2  $k\Omega$  resistor can be used to pull the TTL output up as shown in Figure 5. Some types of TTL outputs will only pull up to within two diode drops of  $V_{CC}$ , which is not high enough for 11C90 inputs. The resistor will pull the signal up through the threshold region, although this final rise may be somewhat slow, depending on wiring capacitance. A resistor network that gives faster rise and also lower impedance is shown in Figure 6.

FIGURE 5. Using Internal Pull-Up with TTL Source

FIGURE 6. Faster Low Impedance TTL to ECL Interface

### Functional Description (Continued)

The ECL outputs have no pull-down resistors and can drive series or parallel terminated transmission lines. For short interconnections that do not require impedance matching, a  $270\Omega$  to  $510\Omega$  resistor to  $V_{\mbox{\footnotesize{EE}}}$  can be used to establish the  $V_{\text{OL}}$  level. Both  $V_{\text{CC}}$  pins must always be used and should

be connected together as close to the package as possible. Pin 12 must always be connected to the V<sub>EE</sub> side of the supply, while pin 13 is required only if the TTL output is used. Low impedance  $V_{CC}$  and  $V_{EE}$  distribution and RF bypass capacitors are recommended to prevent crosstalk.

## Logic Diagram 11C90

TL/F/9892-6

Note: This diagram is provided for understanding of logic operation only. It should not be used for evaluation of propagation delays as many internal functions are achieved more efficiently than shown.

#### Count Sequence Table 11C90

| _     | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> | Q <sub>4</sub> (QTTL)                           |

|-------|----------------|----------------|----------------|-------------------------------------------------|

|       | Н              | Н              | н              | H <b>⋖</b> ———————————————————————————————————— |

| ÷10 , | - <b>,►</b> L  | Н              | Н              | н                                               |

| ŀ     | L              | L              | Н              | н                                               |

| 1     | L              | L              | L              | н                                               |

| Ì     | Н              | L              | L              | н                                               |

|       | н              | н              | L              | н                                               |

|       | L              | Н              | Н              | L                                               |

| ļ.    | L              | L              | Н              | L                                               |

| ł     | L              | L              | L              | L                                               |

| ŀ     | Н              | L              | L              | L                                               |

| Ĺ     | H              | Н              | L              | L ————                                          |

# Operating Mode Table 11C90

|    | Inp | Output         |                |          |

|----|-----|----------------|----------------|----------|

| MS | CE  | M <sub>1</sub> | M <sub>2</sub> | Response |

| Н  | Х   | Х              | Х              | Set HIGH |

| L  | Н   | X              | X              | Hold     |

| L  | L   | L              | L              | ÷11      |

| L  | L   | Н              | X              | ÷10      |

| L  | L   | X              | Н              | ÷10      |

H = HIGH Voltage Level L = LOW Voltage Level X = Don't Care

TL/F/9892-7

Note: A HIGH on MS forces all Qs HIGH.

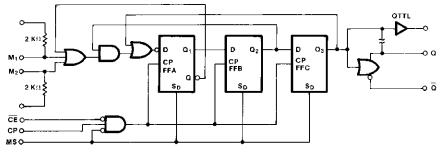

# Logic Diagram 11C91

TL/F/9892-8

Count Sequence Table 11C91

|    | Q <sub>1</sub> | Q <sub>2</sub> | Q3(QTTL)       |

|----|----------------|----------------|----------------|

|    | н              | Н              | н <b>⊸—</b> ÷6 |

| ÷5 | <b>→</b> L     | Н              | н              |

|    | L              | L              | н              |

|    | L              | L              | L              |

|    | Н              | L              | L              |

| L  | — H            | Н              |                |

|    |                |                |                |

Operating Mode Table 11C91

|    | Inp | Output         |                |          |

|----|-----|----------------|----------------|----------|

| MS | CE  | M <sub>1</sub> | M <sub>2</sub> | Response |

| Н  | Х   | Х              | Х              | Set HIGH |

| L  | Н   | X              | X              | Hold     |

| L  | L   | L              | L              | ÷6       |

| L  | L   | X              | Н              | ÷5       |

| L  | L   | Н              | X              | ÷5       |

H = HIGH Voltage LevelL = LOW Voltage Level

Note: A HIGH on MS forces all Qs HIGH.

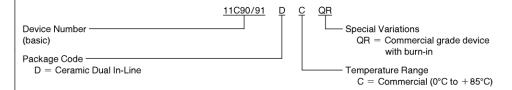

#### **Ordering Information**

The device number is used to form part of a simplified purchasing code where the package type and temperature range are defined as follows:

#### Physical Dimensions inches (millimeters) 0.220-0.310 0.037 ± 0.005 [0.94 ± 0.13] TYP 0.290-0.320 [7.37-8.13] 0.005 [0.13] GLASS SEALANT MIN TYP 0.200 0.180 MAX [5.08] MAX TYP A 0.125-0.200 TYP — [3.18-5.08] TYP — 0.080 MAX BOTH ENDS 95°±5° • TYP 90°± 4° 0.310-0.410 [7.87-10.41] JISA (REV.L) 0.100 ± 0.010 [2.54 ± 0.25] 16 Lead Ceramic Dual-In-Line Package (D) NS Package Number J16A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: oilyge@tevm2.nsc.com

Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 78 35 Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408